monkeywithbrain

monkeywithbrain

Sample and Hold Models in Verilog-A

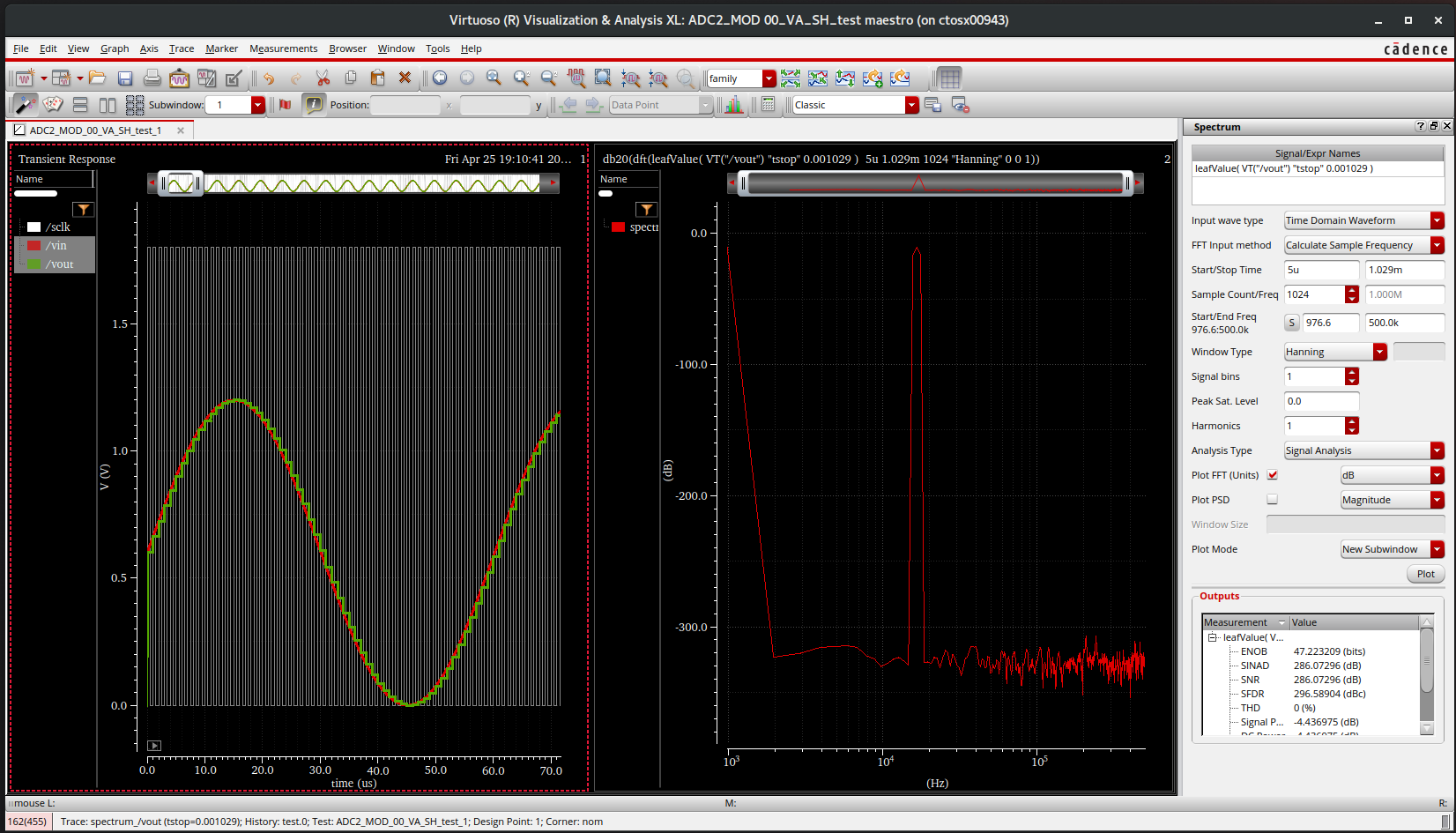

This page demonstrates Verilog-A code examples for Sample and Hold circuits in both current mode and voltage mode, which are commonly used in analog signal processing to sample an input signal at specific intervals and hold it for a certain duration.

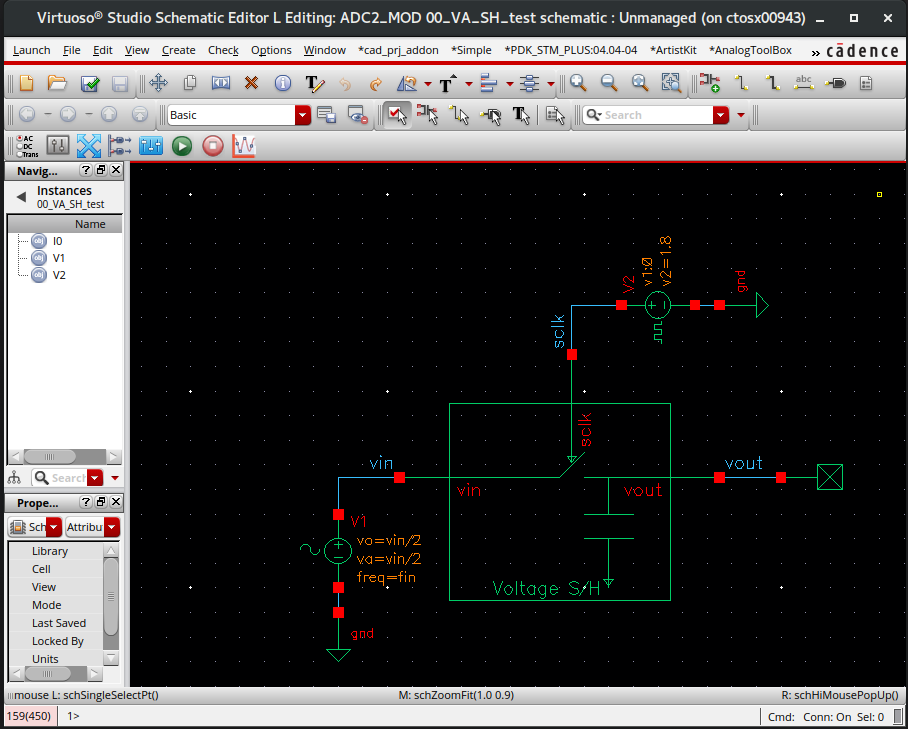

Create a Schematic with the verilogA block

A sample clock based on the sample rate or sample period

An input sinusoid with fin and peak to peak vin

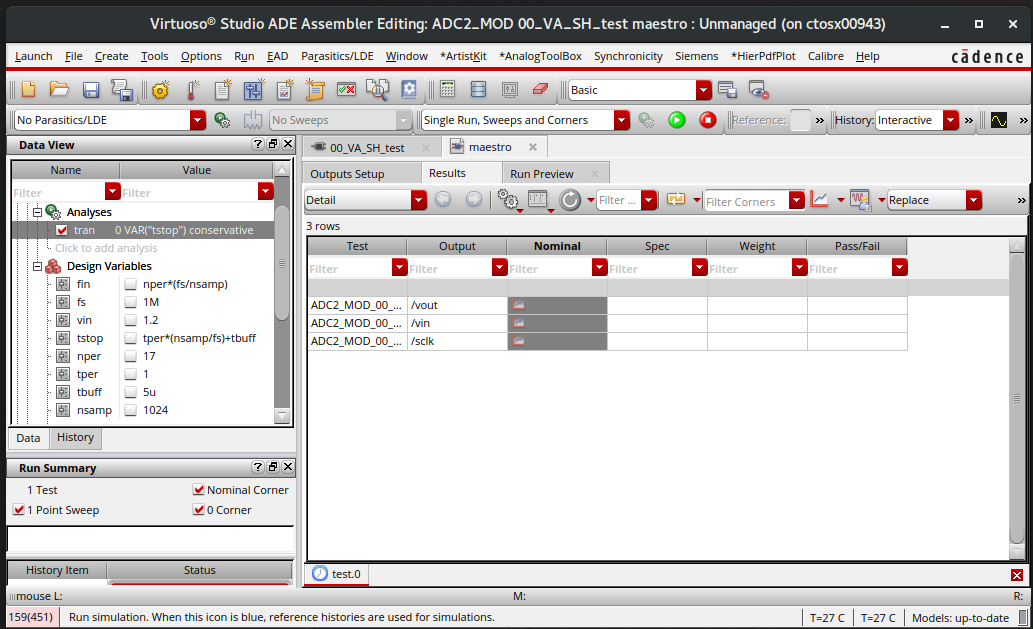

Simulate with the parameters shown in ADE

In this case it is done using ADE Assembler. Anything can be used.

fin =

The input sinusoidal frequency.

nper:

Number of periods. Make sure this is a prime number.

fs:

Sample rate or 1/sampling time

nsamp:

Number of samples, keep this in power of 2. Here it is 2^10. The higher the power of 2 (samples), slower the simulation and more accurate.

tper:

Hom much of the whole period you want to see [0, 1] = [ 0, 100%] : If your simulation is long, this may be useful.

tbuff:

To skip a period of time, for transient response. Select this based on your non-ideal circuit.

tstop:

The transient time period in the tran simulation, put: VAR("tstop")

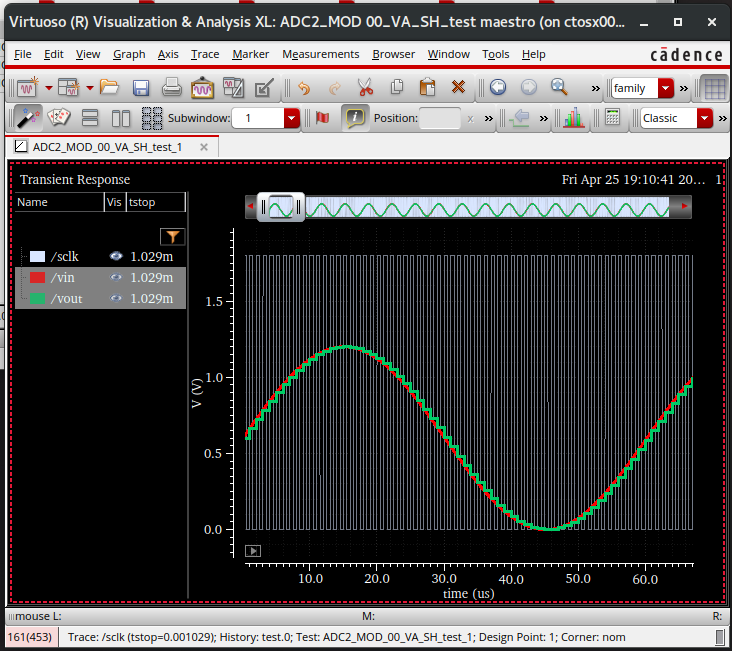

Output of the block

Spectrum validating that it is an ideal block

How to plot a spectum? You will find a plethora of tutorials on the web.

Current Mode Sample and Hold

// VerilogA for SampleAndHold (Current Mode) //nishanchettri `include "constants.vams" `include "disciplines.vams" module current_sample_hold( sclk, iin, iout ); parameter real td = 0; parameter real tr = 2p; parameter real edge_type = 1; parameter real clk_thr = 0.9; input sclk, iin; output iout; electrical iout, iin, sclk; real i; analog begin // Sampling Phase (+1 is for rising edge, -1 is for falling edge) @(cross(V(sclk) - clk_thr, edge_type)) begin i = I(iin); end I(iout) <+ transition(i, td, tr); // V(iout) <+ transition(Vbias, td, tr); // If the output of this block needs a bias end endmodule

Voltage-Mode Sample and Hold

// VerilogA for SampleAndHold (Voltage Mode) //nishanchettri `include "constants.vams" `include "disciplines.vams" module voltage_sample_hold( sclk, vin, vout ); parameter real td = 0; parameter real tr = 2p; parameter real edge_type = 1; parameter real clk_thr = 0.9; input sclk, vin; output vout; electrical vout, vin, sclk; real v; analog begin // Sampling Phase (+1 is for rising edge, -1 is for falling edge) @(cross(V(sclk) - clk_thr, edge_type)) begin v = V(vin); end V(vout) <+ transition(v, td, tr); // V(vout) <+ transition(Vbias, td, tr); // If the output of this block needs a bias end endmodule